Page 12 - 《精细化工》2022年第11期

P. 12

·2162· 精细化工 FINE CHEMICALS 第 39 卷

[5]

粉化等问题产生 [3-4] 。因此,研究者利用硅纳米线 、 化合物,而脱/嵌锂过程则是非晶相锂硅合金与非晶

[6]

[7]

硅纳米管 、互联空心硅纳米球 和硅纳米片等结构 态硅之间的转变,且室温下硅形成合金化程度最高

+

提高了 Li 的存储容量和循环性能。但硅纳米化也带 相为 Li 15 Si 4 ,其理论比容量为 3579 mA·h/g。具体储

来了严重问题,首先在材料的制备方面,工艺较为 锂机理可用式(1)、(2)进行表示:

–

+

复杂,且纳米硅团聚较为明显。此外,随着硅材料 4Si+15Li +15e ↔Li 15 Si 4 (室温) (1)

+

–

尺寸的减小,比表面积会增加,这使得硅与电解液 5Si+22Li +22e ↔Li 22 Si 5 (高温) (2)

接触面积增加,不可逆副反应亦增多,形成较多的

+

固相电解质界面(SEI)膜,导致 Li 的不可逆损失

增多,而且纳米结构通常具有较低的振实密度。除

了硅负极尺寸变化的影响外,材料端 Si 负极表界/

面的性质是下一代锂离子电池应用的另一个重要研

[8]

究点。LAI 等 通过硅烷气体热解合成两种表面结

构不同(粗糙/光滑界面)的硅纳米颗粒,这两种硅

纳米颗粒表面形态的差异导致了材料具有不同的体

积膨胀,影响了 SEI 膜的形成,从而影响了电极的

[9]

寿命。YIN 等 通过观察 Si 锂化前 SEI 膜的形成,

从形态和机制分析这种动态 SEI 膜的电化学形成, [11]

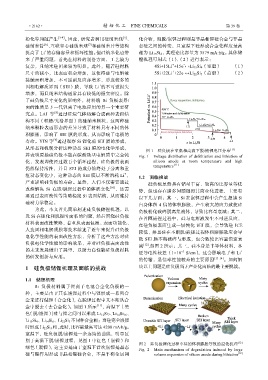

图 1 硅负极在室温和高温下脱/嵌锂电压分布

并表明原始硅负极不能在碳酸盐基电解质中完全钝 Fig. 1 Voltage distribution of delithiation and lithiation of

化,发现即使经过数百个循环过程,硅负极的表面 silicon anode at room temperature and high

temperature [11]

仍然保持活性,并且 SEI 的成分始终处于分离和重

+

组动态变化中,这种动态的 SEI 膜层不断消耗 Li , 1.2 面临挑战

严重影响硅负极的寿命。显然,人们不仅需要通过 硅负极虽然具有储量丰富、较高的比容量等优

改性解决 Si 在嵌/脱锂过程中的体积变化 [10] ,还需 势,但也存在诸多问题阻碍其商业化进程,主要有

要通过表面改性等策略稳定 Si 表面结构,从而维持

以下几方面:其一,Si 在嵌锂过程中会产生超越 Si

硅动力学稳定。

自身体积 4 倍的体积膨胀,产生较大的应力致使硅

为此,本文首先简单阐述硅负极储锂机理,以

负极粉化破碎脱离集流体,导致比容量衰减;其二,

及 Si 在锂化和脱锂时面临的问题,然后围绕硅负极

在首圈嵌锂过程中,硅与电解液发生不可逆反应,

材料表面改性策略,着重从表面包覆、表面功能化、

在硅负极表面生成一层钝化 SEI 膜,会导致硅 ICE

人造固相电解质膜等技术综述了近年来提升硅负极

较低,并且硅在不断脱/嵌锂过程体积膨胀效应会导

电化学性能的表面改性方法,分析了这些方法对硅

致 SEI 膜不断破碎与形成,也会致使比容量快速衰

负极电化学性能的影响效果,并对硅负极表面改性

减 [12] ,如图 2 所示;其三,硅本身是半导体材料,本

的未来发展做出了展望,以助力高性能硅负极材料

–3

征导电性较差(1×10 S/cm),这会影响电子和 Li +

的研发创新与应用。

的传输,是倍率性能较差的主要原因 [13-14] 。如何解

1 硅负极储锂机理及面临的挑战 决以上问题是硅负极当下产业化面临的最主要挑战。

1.1 储锂机理

Si 负极材料属于锂离子电池合金化负极的一

种,主要是由于其在嵌锂过程中与锂形成一系列合

金来进行储锂(合金化),在脱锂过程中又不断从合

金中脱去(去合金化)。如图 1 所示 [11] ,高温下〔黑

色(脱/嵌锂)〕硅与锂之间可以形成 Li 12 Si 7 、Li 14 Si 16 、

Li 13Si 4、Li 14Si 6、Li 22Si 5 不同种合金相;当硅完全嵌锂

时形成 Li 22Si 5 相,此时,比容量最高可达 4200 mA·h/g。

室温下,硅负极脱/嵌锂是一条连续的曲线,明显区

别于高温下脱/嵌锂过程,见图 1 中红色(嵌锂)和

图 2 硅负极锂化过程中硅的体积膨胀导致的退化机理 [12]

绿色(脱锂),这主要是由于室温下首次嵌锂是晶态 Fig. 2 Main mechanism of degradation induced by large

硅与锂作用形成非晶相锂硅合金,不是平衡金属间 volume expansion of silicon anode during lithiation [12]